What is Ultra-HDI?

There is a lot of conversation about “Ultra-HDI” especially with all of the anticipated work being done as part of the CHIPS Act. In my experience, Ultra-HDI means different things to different people depending on where their capabilities and expertise are. IPC has created a working group to address ultra-HDI and their position is that to be considered ultra-HDI, a design needs to include one or more of the following parameters:

Line width below 50 microns

- Spacing below 50 microns

- Dielectric thickness below 50 microns

- Micro via diameter below 75 microns

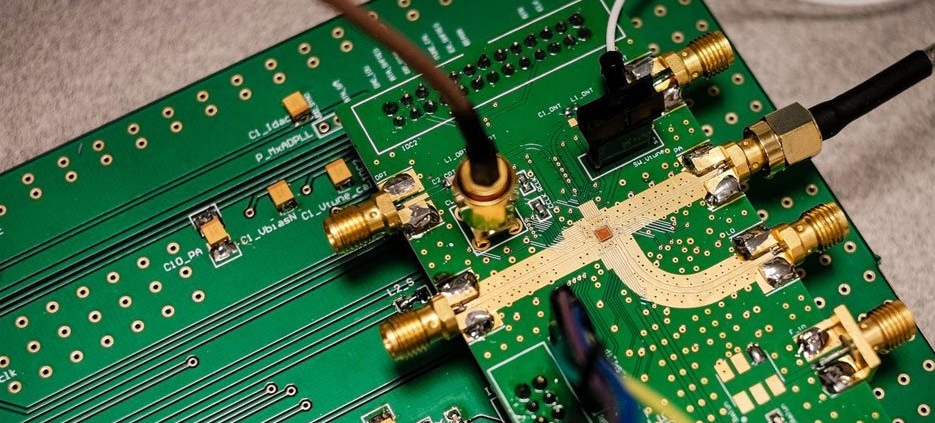

That is a pretty generous definition and there are a few specialized fabricators today that can produce printed circuit boards that meet this criteria using the traditional subtractive etch processes. While using a 50 micron trace and space is an improvement over the traditional 75 micron minimums that we have historically been limited to, I think where it becomes much more interesting is when we are now seeing fabricators that have the capability to create layers with 15 micron line and space. Several fabricators are now building with semi-additive PCB fabrication techniques (SAP) including fabricators that specialize in high-mix low volume work. We have traditionally seen SAP processes run in primarily high-volume facilities.

Even if we don’t push the boundary all the way to 15 micron, using a 25 micron trace and space to break out of tight BGA areas has so many benefits:

- Dramatic size and weight reduction over current state-of-the-art

- Tight spacing and impedance control (< 5%) for all line widths, from 15 microns and above

- Reduced layer count, micro vias and lamination cycles – for greater reliability

- Aspect ratios greater than 1:1 for metal traces – for improved signal integrity

- RF performance better than traditional subtractive-etch processes

- Reduced costs – especially for complex, high-performance boards

In a previous blog post, we discussed a few of the frequently asked questions as printed circuit board designers navigate the learning curve when doing their first designs utilizing these new capabilities. There is a link included below if you want to check those out.

In this blog, we will continue with a few more frequently asked questions with a design for manufacturability focus. For this discussion, let’s look at applications where printed circuit board designers are using a hybrid-approach to their designing. Certain layers are routed with a 25 micron trace and space to reduce the number of layers needed to route out of tight BGA areas and power and ground layers have much larger features. These power and ground layers are typically produced with subtractive-etch processes. When this approach is used, a common question being asked is:

Can I design Via-In-Pad-Plated-Over (VIPPO) technology with these ultra-fine lines and spaces?

The short answer is yes, with the following guidelines: Via in pad/ plated over structures should be run on non-ultra-high-density layers. Preferably these structures, if needed, should be used in an external power/ground structure with line width of 75 micron (3 mils) and spacing of 125 micron (5 mils). This is due to the multiple plating processes required to produce VIPPO technology.

If via-in-pad is necessary along with the ultra-fine lines externally, then a copper filled micro via should be used to route to the next layer down. This via diameter should be 3 to 4 mils diameter and the dielectric spacing should be no greater than the via diameter, preferably less.

A buried structure may be used if the top and bottom layers of the subassembly do not use ultra-fine line width technology. This via may be filled and plated over.

What is the minimum spacing from trace to pad?

While the copper to copper spacing can add costs in subtractive etch processing, in the semi-additive environment this is not the case.

With inner layers, spacing could be 25 microns or below depending on the technology being used by the PCB fabricator.

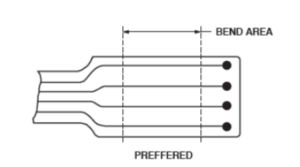

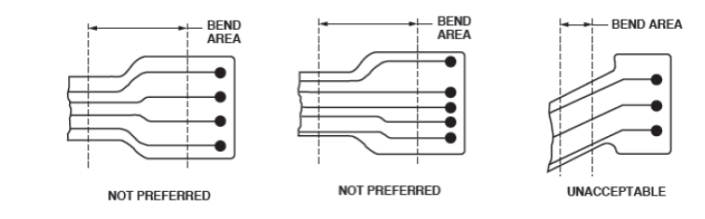

With outer layers, there must be enough space to allow the solder mask to fully cover the trace and not expose any copper. “Mask defined” pads are recommended over “metal defined” pads. This will prevent solder mask registration issues exposing the adjacent metal when the external spacing is less than 75 microns between the pad and adjacent metal.